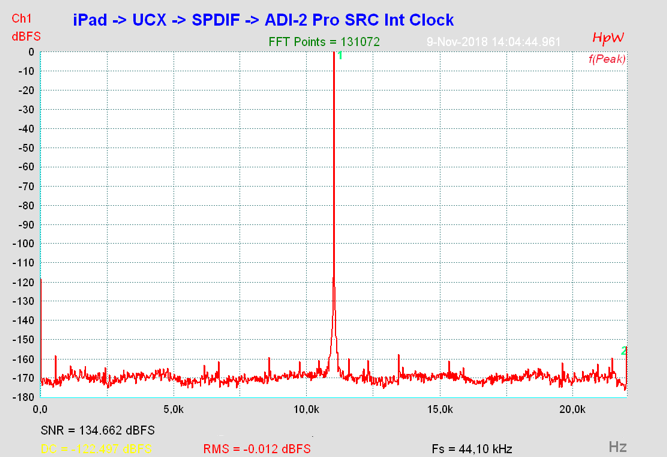

Topic: Jitter issue on the INT clock

I was looking for behaviour of some digital transports on optical input of RME ADI-2 Pro FS.

I was notice a significant jitter raises when I set clock to INT + SRC SPDIF. It even worse than Airport Express as master.

Arta and MusicScope software are used as measurement software in 24 and 16bit modes.

Airport Express (Clock SPDIF, SRC-off):

Airport Express (Clock SPDIF, SRC-on):

Airport Express (Clock INT, SRC-on):

It looks same on other digital transports. Its a wrong mode maybe or I doing something wrong?